**Research Articles**

# Nine-level Cascaded H-Bridge Multilevel Inverter for Photovoltaic Sources Based on Hybrid Active Filter

# Adli Ikhwan<sup>1</sup>, Tze-Zhang Ang<sup>1,\*</sup> and Mohamed Salem<sup>1</sup><sup>10</sup>

<sup>1</sup>Affiliation 1; School of Electrical and Electronic Engineering, Universiti Sains Malaysia (USM), Nibong Tebal, 14300, Penang, Malaysia.

adli\_ikhwan@student.usm.my, salemm@usm.my

\*Correspondence: angtzezhang@student.usm.my;

Citation: Ikhwan, A. Ang, T.Z. Salem, M., "Nine-level Cascaded H-Bridge Multilevel Inverter for Photovoltaic Sources Based on Hybrid Active Filter" *International Journal of Energy and Power Systems*, vol. 1, pp. 6-11, YYY. https:// doi.org/10.54616/ijeps/20220302

Academic Editor: Firstname Lastname Received: 12/01/2022 Accepted: 7/02/2022 Published: 8/02/2022

**Publisher's Note:** IJEPS stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2022 by the authors. Submitted for open access publication under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

# 1. Introduction

High power device has been employed in industrial applications in recent years due to megawatt power level for many medium and high voltage applications[1]. Multilevel power converters are being used as an alternative solution in these applications as a result of this situation [2]. Akagi and Nabae have introduced the basic topology of the multilevel inverter from a three-level inverter in 1981 and the converters known as multilevel inverters (MLIs) have been recoregnised as the most suitable topology for high power applications [3]. AC voltage synthesis of the DC bus from several different voltage levels is the basis of multilevel inverter technology. More steps are applied to the synthesized output waveform, generating a staircase wave that approaches the sinusoidal wave with minimum harmonic distortion as the number of voltage levels on the DC side increases. Among all existing MLIs, cascaded H-bridge MLIs are the simplest to operate and a modular configuration. The number of voltage levels can be increased without altering the inverter's structure by connecting additional H-bridge modules in sequence [4].

**Abstract:** Nowadays, a multilevel inverter is one of the important devices that provides a practical approach device in power system industries because of its features which are less switching losses, lower electromagnetic interference, reduced harmonic distortion, higher DC link voltages, and improved output voltage and current waveforms. Among all existed multilevel inverter, cascaded H-bridge multilevel inverter is the most attractive because of the technology development with megawatt power level. So, the cascaded H-bridge multilevel inverter has been tested and proven as a suitable DC/AC device for medium and high power applications such as renewable energy systems, electric vehicles, and motor drive applications. In this paper, the project is focusing on the combination of a nine-level cascaded H-bridge multilevel inverter connected to photovoltaic (PV) sources and a hybrid power filter. This project aims to study and to analyze the results of the proposed system. The behaviour and the performance of the designed system have shown that the system offered 330V peak output AC voltage with an efficiency of 93.96% and a 5% reduction of THD. This project will be carried out only in Matlab/Simulink software.

Keywords: Multilevel inverter; cascaded H-bridge; PV sources; hybrid power filter;

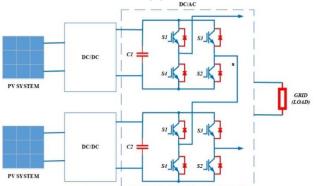

These inverter topologies are particularly ideal for Photovoltaic (PV) applications since different DC voltage levels can easily be provided due to the modular structure of PV arrays[5]. This type of inverter not only achieves low power ratings but also enables the use of renewable energy sources such as photovoltaic cells can be easily interfaced with the system for a high power application [6]. PV inverter is considered the heart of the PV system. A power inverter has to be used to interface photovoltaic modules with the electricity grid system which must perform two tasks, inject a sinusoidal current into the grid and ensure that the PV modules operate at the maximum power point (MPP) [7]. The basic topology of PV systems using a cascaded H-bridge multilevel inverter is shown in Figure 1. A DC-DC boost converter to step up the output voltages.

Power electronic converters for high power control have drastically popular today that lead to non-linear loads in nature that draw non-sinusoidal currents from the utility, resulting in voltage distortion, unwanted currents, extra losses, and device heating in the power system. Due to these situations, various harmonic mitigation techniques have been introduced such as passive power filters (PPFs), active power filters (APFs), and hybrid power filters (HPFs) [8]. HPFs are the combination of PPFs and APFs and they can provide an effective harmonic and reactive power compensation overcoming the technical disadvantages of the other two filters which made them the best choice. The shunt connection of HPF is used to reduce the filter bandwidth requirement of the active filter [9].

Figure 1. Basic topology of PV systems using a cascaded H-bridge multilevel inverter [10]

#### 2. Literature Review

# A. Nine-level Cascaded H-bridge multilevel inverter

Cascaded H-bridge multilevel inverter (CHB-MLI) is the most promising topology for high power. Even low power applications can be implemented using this MLI. This is due to no capacitors or diodes requirement for clamping purpose and the output waveform is considered sinusoidal without a filtering processs . The zero harmonic distortion of output waveform can be achieved with an infinite number of levels, but constraints by voltage unbalance problem, circuit layout, and limitation of power factor level [11]. This inverter is made up of multiple single-phase H-bridge cells bound in sequence. Using different DC sources, this structure is capable of generating high voltage levels at the output side. CHB operates at a high switching frequency and generates a nearly sinusoidal output waveform [12]. This waveform is typical of n-level CHB-MLI which looks like a staircase waveform. The voltage will be in form of zero, positive-cycle, and negative-cycle.

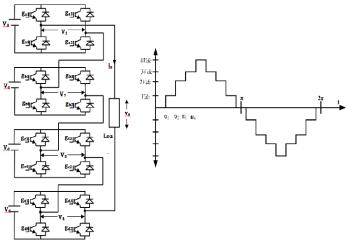

The nine-level CHB-MLI will produce nine levels of AC output voltage. This circuit is formed by connecting four separate sources of input DC voltage to the series of four H-bridge cells controlled by switches by referring to Figure 2 which will operate in toggle operation. Sixteen main switch devices are included for a series-connected nine-level H-bridge configuration,  $S_1$ ~ $S_4$ ,  $S_5$ ~ $S_8$ ,  $S_9$ ~ $S_{12}$ , and  $S_{13}$ ~ $S_{16}$  [13]. The toggle operation is resulting in Table 2.2. The table shows the sets of switches that need to be triggered to generate the required output voltage. The nine levels of output voltage are +4V<sub>dc</sub>, +3V<sub>dc</sub>, +2V<sub>dc</sub>, +V<sub>dc</sub>, 0, -V<sub>dc</sub>, -2V<sub>dc</sub>, -3V<sub>dc</sub>, -4V<sub>dc</sub>.

# Table I Toggle operation of nine-level CHB-MLI

| Vo                | S <sub>1</sub> | $S_2$ | $S_3$ | $S_4$ | S <sub>5</sub> | S <sub>6</sub> | $S_7$ | S <sub>8</sub> | S <sub>9</sub> | S <sub>10</sub> | S11 | S <sub>12</sub> | S <sub>13</sub> | S14 | S <sub>15</sub> | S16 |

|-------------------|----------------|-------|-------|-------|----------------|----------------|-------|----------------|----------------|-----------------|-----|-----------------|-----------------|-----|-----------------|-----|

| $+4V_{dc}$        | 1              | 1     | 0     | 0     | 1              | 1              | 0     | 0              | 1              | 1               | 0   | 0               | 1               | 1   | 0               | 0   |

| $+3V_{de}$        | 1              | 1     | 0     | 0     | 0              | 1              | 0     | 0              | 1              | 1               | 0   | 0               | 1               | 1   | 0               | 0   |

| $+2V_{de}$        | 1              | 1     | 0     | 0     | 0              | 1              | 0     | 0              | 0              | 1               | 0   | 0               | 1               | 1   | 0               | 0   |

| $+V_{dc}$         | 1              | 1     | 0     | 0     | 0              | 1              | 0     | 0              | 0              | 1               | 0   | 0               | 0               | 1   | 0               | 0   |

| $0V_{dc}$         | 0              | 1     | 1     | 0     | 0              | 1              | 1     | 0              | 0              | 1               | 1   | 0               | 0               | 1   | 1               | 0   |

| $0V_{dc}$         | 1              | 0     | 0     | 1     | 1              | 0              | 0     | 1              | 1              | 0               | 0   | 1               | 1               | 0   | 0               | 1   |

| -Vde              | 0              | 0     | 1     | 1     | 0              | 0              | 1     | 0              | 0              | 0               | 1   | 0               | 0               | 0   | 1               | 0   |

| -2V <sub>dc</sub> | 0              | 0     | 1     | 1     | 0              | 0              | 1     | 0              | 0              | 0               | 1   | 0               | 0               | 0   | 1               | 1   |

| $-3V_{de}$        | 0              | 0     | 1     | 1     | 0              | 0              | 1     | 0              | 0              | 0               | 1   | 1               | 0               | 0   | 1               | 1   |

| -4V <sub>dc</sub> | 0              | 0     | 1     | 1     | 0              | 0              | 1     | 1              | 0              | 0               | 1   | 1               | 0               | 0   | 1               | 1   |

Figure 2. Circuit configuration of nine-level H-bridge multilevel inverter and output waveform [14]

# B. PV Panel

The photovoltaic (PV) panel is constituted by sets of PV cells. PV cell is the basic structural unit of the photovoltaic module that generates current carriers when sunlight falls on it which consists of a p-n junction and converts light energy directly into electrical energy. The PV modules generate the current and voltage in DC [15]. PV modules are rated at a set of conditions known as Standard Test Conditions (STC), which specifies a cell temperature of 25 °C and an irradiance of 1000 W/m<sup>2</sup> with an AM 1.5 spectrum. The peak point at which maximum energy is generated from the PV panel is called Maximum Power Point (MMP) [16]. The amount of solar radiation received by the panels is known to affect the amount of energy produced by the PV cells [17].

# C. DC-DC Converter

A DC-DC converter also known as a DC chopper is a static system that converts a fixed DC voltage to a variable DC voltage [18]. The device is commonly used to provide a regulated output voltage to electric and electronic circuits [19]. Isolated converters and non-isolated converters are the two main types of DC-DC converters. Non-isolated DC-DC boost (step-up) converter is capable of generating an output voltage that is higher than the input voltage which especially significant in the wide range of applications of energy sources with flexible input voltage range and low output voltage such as photovoltaic panels and fuel cells. Switching frequency,  $f_s$ selection is usually 20kHz or higher to avoid acoustic noise and to reduce the size of the inductor and capacitor. But, if the  $f_s$  is set too high, it will cause high switching loss and heat which leads to low efficiency. The current ripple,  $\Delta i_L$  is supposed to be 20% to 40% of input current and voltage ripple,  $\Delta v_c$  is 0.5% to 5% of output voltage [14]. Direct current to direct current (DC/DC) converters are required to have higher voltage gains in some applications for electric vehicles, highvoltage level charging systems and fuel cell electric vehicles. Therefore, it is greatly important to carry out research on high

voltage gain DC/DC converters. To improve the efficiency of high voltage gain DC/DC converters and solve the problems of output voltage ripple and robustness, this paper proposes a double-boost DC/DC converter. Based on the small-signal model of the proposed converter, a double closed-loop controller with voltage–current feedback and input voltage feedforward is designed. The experimental results show that the maximum efficiency of the proposed converter exceeds 95%, and the output voltage ripple factor is 0.01. Compared with the traditional boost converter and multi-phase interleaved DC/DC converter, the proposed topology has certain advantages in terms of voltage gain, device stress, number of devices, and application of control algorithms.

# D. Hybrid Power Filter

Hybrid power filter (HPF) topology is supposed to enhance harmonics and reactive power compensations. When it comes to power factor correction, the HPF has a significant advantage over capacitor banks because it can fine-tune reactive consumption [20]. The HPF is a synergistic combination of passive and active filters that is appealing. So, for load harmonic compensations, various hybrid filters with various control systems have been proposed [21].

### 4. Methodology

# A. System Design

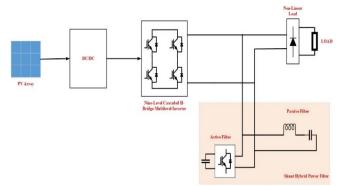

A system that is required to be designed by using Matlab/Simulink software was an AC single-phase system with solar energy at STC as its source. Hence, the load voltage is set to 230V RMS value and the frequency of 50 Hz as given by the Energy Commission of Malaysia [22]. The proposed design of the project is shown in Figure 3 with the constant  $1000W/m^2$  of irradiance and  $25^{\circ}C$  of temperature are connected to PV panels.

Figure 3. Proposed circuit design of the project

# B. Project Implementation Flow

The nine-level CHB-MLI is designed by connecting four sets of H-bridge circuits which each set consists of four switching devices. So, the 16 switching devices are needed with four DC sources. IGBT is chosen as a switching device because of its high current carrying capability, gate control using voltage rather than current, as well as the ability to match the co-pack diode with IGBT. The firing angle, phase angle, and pulse width are set as equations below:

Levels of inverter,

$$m = 2s + 1$$

(1)

No of source

$$=\frac{(m-1)}{2}$$

(2)

Firing angle,

$$a_i = \frac{i \times 180}{m}$$

(3)

$$Phase \ delay = \frac{period \times a_i}{360} \tag{4}$$

$$Pulse width = \frac{Difference \ between \ periods \ during \ on-state,s}{Total \ period,s} \times$$

*m* is representing levels of output voltage, *s* is the number of switches or semiconductors, and *i* is the number of sources. The result is tabulated in Table 2. Table  $\mathbf{II}$

| $ \begin{array}{ c c c c c c c c } \hline Switching Time Table of Multilevel Inverter \\ \hline \hline V_{evt} & Angle & Phase S1, S1, S1, S1, S2, S1, S1, S1, S1, S1, S1, S1, S1, S1, S1$                                        | S:                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                            | S                            |

| 1Vs         40         0.0022           2Vs         60         0.0033                                                                                                                                                             |                              |

| 2Vs 60 0.0033                                                                                                                                                                                                                     |                              |

|                                                                                                                                                                                                                                   |                              |

| 3Vs 80 0.0044                                                                                                                                                                                                                     |                              |

|                                                                                                                                                                                                                                   |                              |

| 4Vs         100         0.0056         Pulse         Pulse         Pulse           Width         Width         Width         Width         Width           =         =         38.89%         27.78%         16.67%         5.56% |                              |

| 3Vs 120 0.0067                                                                                                                                                                                                                    |                              |

| 2Vs 140 0.0078                                                                                                                                                                                                                    |                              |

| 1Vs 160 0.0089                                                                                                                                                                                                                    |                              |

| 0 200 0.011                                                                                                                                                                                                                       |                              |

| -1Vs 220 0.012                                                                                                                                                                                                                    |                              |

| -2Vs 240 0.013                                                                                                                                                                                                                    |                              |

| -3V <sub>8</sub> 260 0.014                                                                                                                                                                                                        |                              |

| Width Width Width 38.89% 27.78% 16.67% 2                                                                                                                                                                                          | Pulse<br>Width<br>=<br>5.56% |

| -3Vs 300 0.017                                                                                                                                                                                                                    |                              |

| -2Vs 320 0.018                                                                                                                                                                                                                    |                              |

| -1Vs 340 0.019                                                                                                                                                                                                                    |                              |

| 0 360 0.02                                                                                                                                                                                                                        |                              |

The PV panel modules that have been used in this project were SPM100-M PV modules by Solar Power Mart and the parameter specifications for each module at STC (25oC, 1000W/m2) are listed in Table III [23]. The output power of each PV equals the input power of a boost converter, 200W. Therefore, two series-connected modules per string are needed for a PV module.

| Table III           SPM100-M PV Panel Module Paramet | arc [23]     |

|------------------------------------------------------|--------------|

| Parameter                                            | Rating       |

| Maximum power (W)                                    | 100          |

| Open-circuit voltage, Voc (V)                        | 22.53        |

| Short-circuit current, Isc (A)                       | 5.70         |

| Voltage at maximum power point, VMPP (V)             | 18.75        |

| Current at maximum power point, IMPP (A)             | 5.34         |

| Cell per module (N <sub>cell</sub> )                 | 36           |

| Parallel strings                                     | 1            |

| Series-connected modules per string                  | 2            |

| Temperature coefficient of Voc((%/°C)                | -0.35 ± 0.02 |

| Temperature coefficient of Isc (%/°C)                | 0.05 ± 0.01  |

The boost converter is designed based on the parameters in Table IV. The input voltage of the converter is two times the

(5)

$V_{OC}$  and the input current of the converter is equals to  $I_{SC}$ . In this project, 20kHz is chosen as switching frequency with 40% current ripple and 5% voltage ripple. The value of duty cycle, resistor, inductor, and capacitor are calculated using these equations:

$$Duty \ cycle, D = 1 - \frac{V_{in}}{V_{out}} = \frac{t_{on}}{T_{sw}}$$

(6)

$$Output \ current, I_{out} = \frac{P_{out}}{V_{out}}, \ resistance, R = \frac{V_{out}}{I_{out}} \ (7)$$

Inductor,

$$L = \frac{V_{in}}{2\Delta i_L} DT_s = \frac{V_{in}D}{f_s\Delta i_L}$$

(8)

$$Capacitor, C = \frac{V_{out}DT_s}{2R\Delta v_C} = \frac{I_{out}D}{f_s\Delta v_C}$$

(9)

Table IV

| Parameter                 | Rating  |

|---------------------------|---------|

| Switching frequency (kHz) | 20      |

| Input voltage (V)         | 45.06   |

| Input current (A)         | 5.70    |

| Output voltage (V)        | 90.32   |

| Output current (A)        | 1.993   |

| Duty cycle (%)            | 49.89   |

| Resistance $(\Omega)$     | 45.32   |

| Inductor (mH)             | 0.4930  |

| Capacitor (µF)            | 11.0087 |

In designing a shunt hybrid filter, a passive filter configuration and an active filter configuration connected in parallel are needed. An active filter circuit is designed by using one set of H-bridge configuration with a constant DC-link capacitor to regulate the switching losses, then ensure the continuous and stable operation of the filter. The duty cycle for the active filter is set to 50% and the frequency equals the frequency of the system, 50Hz. The parameters are set as shown in Table 5. A non-linear load circuit is also being connected parallel to the filters which offers varying impedance to the applied voltage so that the current waveform does not vary according to the voltage waveform.

Table V

Parameters of Hybrid Power Filter

| I arameters of Hybrid Fower Filter |        |  |  |  |

|------------------------------------|--------|--|--|--|

| Parameter                          | Rating |  |  |  |

| Active filter                      |        |  |  |  |

| Frequency (Hz)                     | 50     |  |  |  |

| Duty cycle (%)                     | 50     |  |  |  |

| DC-link capacitor, $C_{dc}$ (µF)   | 1      |  |  |  |

| Passive filter                     |        |  |  |  |

| Inductor, $L_f$ (mH)               | 13     |  |  |  |

| Capacitor, $C_f$ (nF)              | 300    |  |  |  |

| Inverter                           |        |  |  |  |

| Inductor, $L_{inv}$ (mH)           | 0.1    |  |  |  |

| Load                               |        |  |  |  |

| Inductor, L <sub>load</sub> (mH)   | 0.3    |  |  |  |

| Resistor, $R_{load}(\Omega)$       | 180    |  |  |  |

# 4. Result and Discussion

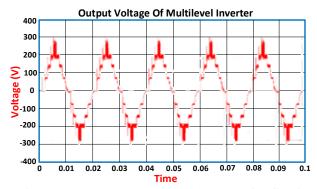

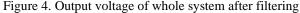

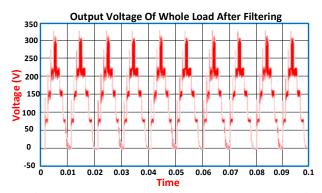

The simulation results have proved the effectiveness of the system by observing its performance. The system's performance has been determined from the voltage, power, efficiency, and THD. This system is capable to generate higher output voltage and power with low voltages and powers are being supplied to the system. The input voltage that is supplied by each PV source is 84.24V and four connected sources have generated 330V output voltage after being filtered and 325.9V output voltage at the load as shown in Figure 4 and Figure 5.

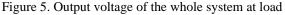

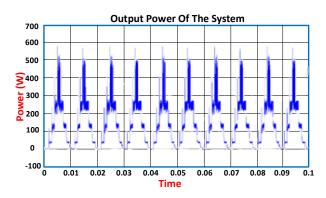

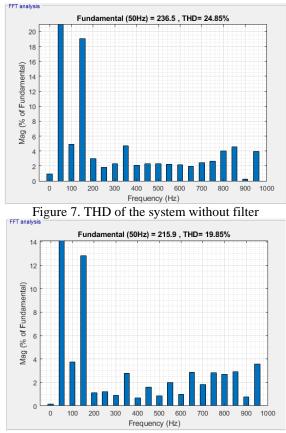

The input power supplied to the system is 156.6W for each source and these input powers can generate the output power until 589.9W. Figure 6 displays the output power of the system. For THD analysis, the percentage of THD is reduced from 24.85% to 19.85% after connecting the filter circuit. These values are proven in Figure 7 and Figure 8 by using FFT analysis. This has proven that the multilevel inverter can be designed without any filtering component because this system can generate an almost ideal sinusoidal outcome in nature. So, the difference in THD is considered small.

Next, the RMS value of the output voltages and the efficiency of the system are calculated by using these equations:

$$Voltage \ in \ RMS \ value, V_{rms} = \frac{V_{peak}}{\sqrt{2}}$$

(11)

Efficiency,

$$\eta = \frac{V_{out}}{V_{in}} \times 100\%$$

(12)

https://iespublication.com

# Figure 6. Output power of the whole system

Table 6 summarizes the performance of the overall system run from the simulation. From the table, this type of multilevel inverter has proven to be one of the most preferable converter devices suitable to be used in medium-high power applications and even in low applications.

Figure 8. THD of the system with filter

Table VI

| Performance of the system |                       |          |        |            |         |  |  |

|---------------------------|-----------------------|----------|--------|------------|---------|--|--|

| Input                     | Output                | Input    | Output | Efficiency | THD     |  |  |

| Voltage                   | Voltage               | Power    | Power  |            |         |  |  |

|                           | After filtering:      |          |        |            |         |  |  |

|                           |                       |          |        |            |         |  |  |

|                           | Peak Voltage=         |          |        |            | Without |  |  |

|                           | 330V <sub>ac</sub>    |          |        |            | filter: |  |  |

|                           | RMS                   | 156.6W   |        |            |         |  |  |

| $84.24V_{DC}$             | Voltage=              | (one     |        |            | 24.85%  |  |  |

| (one                      | 233.35V <sub>ac</sub> | source)  | 589.9W | 93.96%     |         |  |  |

| source)                   |                       | ~        |        |            | With    |  |  |

|                           | At load:              | 627.8W   |        |            | filter: |  |  |

|                           |                       | for four |        |            |         |  |  |

|                           | Peak Voltage=         | sources  |        |            | 19.85%  |  |  |

|                           | 325.9V <sub>dc</sub>  |          |        |            |         |  |  |

|                           | RMS                   |          |        |            |         |  |  |

|                           | Voltage=              |          |        |            |         |  |  |

|                           | 230.45V <sub>dc</sub> |          |        |            |         |  |  |

5. Conclusion

In conclusion, the circuit of a combination of ninelevel cascaded H-bridge multilevel inverter feeds by PV sources with a shunt hybrid power filter has successfully modeled and simulated in Matlab/Simulink software. From the simulation, this type of multilevel inverter has proven to be one of the most preferable converter devices suitable to be used in medium-high power applications and even in low applications. This is because the low input can be improved to a higher level of output and the distortion is also considered low. The higher level of the inverter, the smoother the waveform produced. Moreover, with the low complexity of the circuit configuration, the waveform produced can be said ideally sinusoidal without being filtered. However, the most significant disadvantage for this configuration that we can see in the simulation is the size of the cascaded H-bridge multilevel inverter becomes larger as the number of levels increased. For the PV selection with constant irradiance and temperature, the most suitable PV has to be selected to get the required input value and the DC converter is necessary for the circuit with the renewable energy source.

# 6. Acknowledgement

The authors would like to pay gratitude to Research Creativity and Management Office (RCMO) of the Universiti Sains Malaysia for supporting with funding under the Shortterm grant No. 304/PELECT/6315330, and library facilities. Lastly thanks to those colleagues who have either directly or indirectly contributed to the completion of this work.

# References

[7]

- [1] Alhamrouni, I., et al., Design of single phase inverter for photovoltaic application controlled with sinusoidal pulse width modulation. Indonesian Journal of Electrical Engineering and Computer Science, 2019. 15(2): p. 620-630.

- [2] Bughneda, A., et al., Review of multilevel inverters for PV energy system applications. Energies, 2021. 14(6): p. 1585.

- [3] Waware, M. and P. Agarwal, Hardware realization of multilevel inverter-based active power filter. IETE Journal of Research, 2012. 58(5): p. 356-366.

- [4] Chabni, F., et al., New modified CHB multilevel inverter topology with elimination of lower and higher order harmonics. Automatika, 2018. 59(1): p. 1-10.

- [5] Bughneda, A., et al. A Single-Phase Multilevel Inverter with Reduced Switch Count for Solar PV Application. in 2021 IEEE Conference on Energy Conversion (CENCON). 2021. IEEE.

- [6] Pattathurani, L., R.K. Dwibedi, and D.S. Dash, Multilevel Inverter For Solar Power Applications. International Journal of Engineering Development and Research, 2017. 5(1): p. 684-690.

- Oliveira, K.C., J.L. Afonso, and M.C. Cavalcanti. Multilevel inverter for grid-connected photovoltaic systems with active filtering function. in Doctoral Conference on Computing, Electrical and Industrial Systems. 2013. Springer.

- [8] Varschavsky, A., et al., *Cascaded nine-level inverter for hybrid-series active power filter, using industrial controller.* IEEE Transactions on Industrial Electronics, 2009. 57(8): p. 2761-2767.

- [9] Srivatsav, C., P. Agarwal, and C.V. Avinash. Types of Hybrid Power Filter and their comparative performance analysis with distorted source voltage using MATLAB. in 2014 International Conference on Advances in Energy Conversion Technologies (ICAECT). 2014. IEEE.

- [10] Ghasemi, N., et al. A new unequal DC link voltage configuration for a single phase multilevel converter to reduce low order harmonics. in Proceedings of the 2011 14th European Conference on Power Electronics and Applications. 2011. IEEE.

- [11] Gaikwad, A. and P.A. Arbune. Study of cascaded H-Bridge multilevel inverter. in 2016 International Conference on Automatic Control and Dynamic Optimization Techniques (ICACDOT). 2016. IEEE.

- [12] Gadalla, A.S., et al., Evaluating the capacity of power and energy balance for cascaded H-bridge multilevel inverter using different PWM techniques. The Journal of Engineering, 2017. 2017(13): p. 1713-1718.

- [13] Jalakanuru, N. and M. Kiber, Switching angle calculation By EP HEP HH And FF Methods For Modified 11-Level Cascade H-Bridge Multilevel Inverter. International Journal of Engineering Science Invention (IJESI), 2017. 6(12): p. 69-75.

- [14] Gopal, Y., D. Birla, and M. Lalwani, Selected harmonic elimination for cascaded multilevel inverter based on photovoltaic with fuzzy logic control maximum power point tracking technique. Technologies, 2018. 6(3): p. 62.

- Pandey, N. and D. Karthikeyan, *Design and Analysis of Modular Multilevel Inverter for PV-FED Applications*. International Research Journal of Engineering and Technology, 2016. 3(4): p. 437-442.

- Yusof, N.F.M., D. Ishak, and M. Salem, An Improved Control Strategy for Single-Phase Single-Stage Grid-Tied PV System Based on Incremental Conductance MPPT, Modified PQ Theory, and Hysteresis Current Control. Engineering Proceedings, 2022.

12(1): p. 91.

- [17] Kadhum, J., Design and construction of a tracking device for solar electrical systems. Journal of Scientific and Engineering Research, 2018. 5(7): p. 225-236.

- [18] Alhamrouni, I., et al., *Design and development of SEPIC DC-DC* boost converter for photovoltaic application. International Journal of Power Electronics and Drive Systems, 2019. 10(1): p. 406.

- [19] Mallik, D.I., Design of Isolated DC-DC and DC-DC-AC Converters with Reduced Number of Power Switches. 2017, Purdue University.

- [20] Rodrigues Limongi, L., et al., *Reactive power and current harmonic control using a dual hybrid power filter for unbalanced non-linear loads.* Energies, 2018. **11**(6): p. 1392.

- [21] Omran, M.A., et al. Investigating the ability of shunt hybrid power filter based on SRF method under non-ideal supply voltage.

in IOP conference series: materials science and engineering.

2018. IOP Publishing.

- [22] Commission, E., *Energy Malaysia*. 2014, Energy Commission.

- [23] Pratama, E. and R. Watiasih, Perbandingan Perolehan Daya Solar Panel Monocrystalline Terhadap Solar Panel Polycrystalline. ELKHA: Jurnal Teknik Elektro. 12(2): p. 105-111.